# AD8159 Evaluation Board Application Guide

EVAL-AD8159-AC/DC

#### FEATURES

Facilitates evaluation of the AD8159 Either ac- or dc-coupled versions Optimized layout

#### **GENERAL DESCRIPTION**

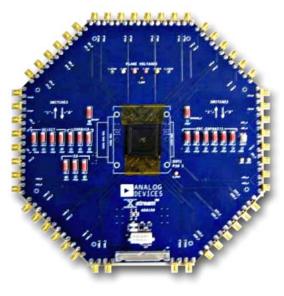

The AD8159 evaluation board consists of 24 differential 100  $\Omega$  microstrip traces on the top layer with side launch SMA connectors. A 10 inch differential microstrip test trace is routed on the bottom layer. Toggle switches are used to select logic high and logic low for the individual control signals. The AD8159 evaluation board is available in either an ac-coupled or dc-coupled version (AD8159-EVAL-AC or AD8159-EVAL-DC). The ac-coupled evaluation board has ac-coupling capacitors installed on all of the gigabit serial I/O ports.

Refer to the AD8159 data sheet in conjunction with this document.

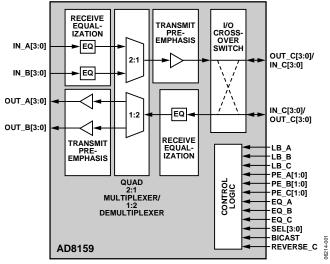

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1. AD8159 Block Diagram

Figure 2. AD8159 Evaluation Board

06214-002

Rev. 0

Evaluation boards are only intended for device evaluation and not for production purposes. Evaluation boards as supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. No license is granted by implication or otherwise under any patents or other intellectual property by application or use of evaluation boards. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Analog Devices reserves the right to change devices or specifications at any time without notice. Trademarks and registered trademarks are the property of their respective owners. Evaluation boards are not authorized to be used in life support devices or systems.

# **TABLE OF CONTENTS**

| Features                  | 1 |

|---------------------------|---|

| General Description       | 1 |

| Functional Block Diagram  | 1 |

| Revision History          | 2 |

| Evaluation Board Hardware | 3 |

| Control Interface         | 3 |

| Power Connector              | 4 |

|------------------------------|---|

| Power Supply Configurations  | 5 |

| AD8159 Evaluation Board Note | 5 |

| Ordering Information         | 6 |

| Ordering Guide               | 6 |

| ESD Caution                  | 6 |

#### **REVISION HISTORY**

3/07—Revision 0: Initial Version

### **EVALUATION BOARD HARDWARE**

#### **CONTROL INTERFACE**

The AD8159 is controlled by 19 individual switches summarized in Table 1. When a toggle switch is in the up position, a Logic 1 is placed on the respective signal. Conversely, a switch in the down position places a Logic 0 on the respective signal. All signals are active high unless otherwise specified. Refer to the AD8159 data sheet for a detailed description of device functionality. Signals on the board labeled SER, SCLK, and RESET are for ADI internal use only.

| Signal    | Description                | Function                                                                                                                           |  |

|-----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| SEL0      | A/B select for Port 0      | 0 selects Port A.<br>1 selects Port B.                                                                                             |  |

| SEL1      | A/B select for Port 1      | 0 selects Port A.<br>1 selects Port B.                                                                                             |  |

| SEL2      | A/B select for Port 2      | 0 selects Port A.<br>1 selects Port B.                                                                                             |  |

| SEL3      | A/B select for Port 3      | 0 selects Port A.<br>1 selects Port B.                                                                                             |  |

| EQ_A      | Equalization setting for A | 0 sets input Port A for low EQ.<br>1 Sets input Port A for high EQ.                                                                |  |

| EQ_B      | Equalization setting for B | 0 sets input Port B for low EQ.<br>1 sets input Port B for high EQ.                                                                |  |

| EQ_C      | Equalization setting for C | 0 sets input Port B for low EQ.<br>1 sets input Port B for high EQ.                                                                |  |

| REVERSE_C | Reverse C enable           | 0 sets Port C I/O pins to input and O/I pins to output signals.<br>1 sets Port C I/O pins to output and O/I pins to input signals. |  |

| BICAST    | Bicast enable              | 0 sets the mux in unicast mode.<br>1 sets the mux in bicast mode.                                                                  |  |

| PE0_A     | Pre-emphasis LSB for A     | PE_A [1:0] = 00 sets PE on output Port A to no pre-emphasis.<br>PE_A [1:0] = 01 sets PE on output Port A to low pre-emphasis.      |  |

| PE1_A     | Pre-emphasis MSB for A     | PE_A [1:0] = 10 sets PE on output Port A to mid pre-emphasis.<br>PE_A [1:0] = 11 sets PE on output Port A to high pre-emphasis.    |  |

| PEO_B     | Pre-emphasis LSB for B     | PE_B [1:0] = 00 sets PE on output Port B to no pre-emphasis.<br>PE_B [1:0] = 01 sets PE on output Port B to low pre-emphasis.      |  |

| PE1_B     | Pre-emphasis MSB for B     | PE_B [1:0] = 10 sets PE on output Port B to mid pre-emphasis.<br>PE_B [1:0] = 11 sets PE on output Port B to high pre-emphasis.    |  |

| PE0_C     | Pre-emphasis LSB for C     | PE_C [1:0] = 00 sets PE on output Port C to no pre-emphasis.<br>PE_C [1:0] = 01 sets PE on output Port C to low pre-emphasis.      |  |

| PE1_C     | Pre-emphasis MSB for C     | PE_C [1:0] = 10 sets PE on output Port C to mid pre-emphasis.<br>PE_C [1:0] = 11 sets PE on output Port C to high pre-emphasis.    |  |

| LB_A      | Loopback enable for A      | 0 sets Port A in normal mode.<br>1 sets Port A in loopback mode.                                                                   |  |

| LB_B      | Loopback enable for B      | 0 sets Port B in normal mode.<br>1 sets Port B in loopback mode.                                                                   |  |

| LB_C      | Loopback enable for C      | 0 sets Port C in normal mode.<br>1 sets Port C in loopback mode.                                                                   |  |

<sup>1</sup> Note that the select function is controlled on a lane-by-lane basis, whereas the rest of the features are set on a port-by-port basis.

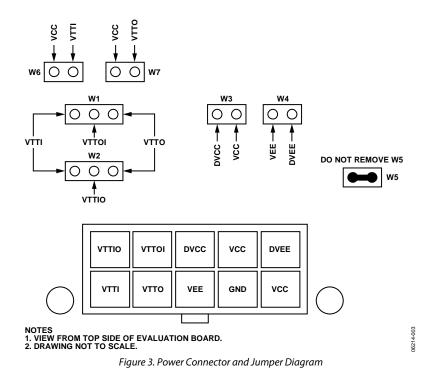

#### **POWER CONNECTOR**

The AD8159 evaluation board is supplied with a power cable. The individual conductors in the power cable are color coded as described in Table 2.

All supplies can be connected to a common 3.3 V supply or can be connected to separate supplies to monitor independent supply

Table 2. Power Cable Summary

currents. Jumpers are provided to connect VTTOI to either VTTI or VTTO (W1), VTTIO to either VTTI or VTTO (W2), DVCC to VCC (W3), DVEE to VEE (W4), VTTI to VCC (W6), and VTTO to VCC (W7). W5 shorts the level-shifting diode, CR5, and should not be removed. The power connector pin assignments and jumper pin assignments are illustrated in Figure 3.

| Power Supply | Color  | Description                                   |  |

|--------------|--------|-----------------------------------------------|--|

| VCC          | Red    | Core supply                                   |  |

| VEE          | White  | Return for core and term                      |  |

| VTTI         | Yellow | Input termination supply (Port A and Port B)  |  |

| VTTO         | Green  | Output termination supply (Port A and Port B) |  |

| VTTIO        | Orange | Input/output termination supply for Port C    |  |

| VTTOI        | Blue   | Output/input termination supply for Port C    |  |

| GND          | Black  | Reference plane supply                        |  |

| DVCC         | Gray   | Pull-up supply for toggle switches            |  |

| DVEE         | White  | Pull-down supply for toggle switches          |  |

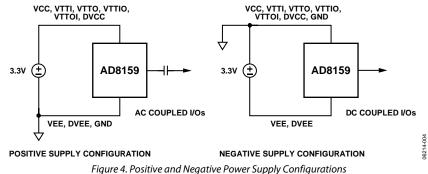

#### **POWER SUPPLY CONFIGURATIONS**

The differential I/O signals are routed on microstrips on the top layer of the board. Trace widths, spacing, and dielectric thickness were designed for a 100  $\Omega$  differential impedance. The reference plane (GND) is not electrically connected to VEE, allowing the board to be configured with either positive or negative supplies. The negative supply configuration is useful when connecting the AD8159 to test equipment that has a 50  $\Omega$  termination to GND. The positive and negative supply configurations are illustrated in Figure 4.

#### **AD8159 EVALUATION BOARD NOTE**

An issue with uncorrelated chatter may be observed at the outputs of active lanes if the corresponding inputs are left unconnected. This can lead to crosstalk in adjacent lanes.

#### Explanation

The high sensitivity of the receiver causes the device to amplify noise if the inputs are left unconnected (floating).

#### Solution

Install a 1 k $\Omega$  to 2 k $\Omega$  pull-down resistor from one side of the unused differential pairs (P or N) to VEE. This adds a static offset voltage (nonzero differential input voltage) and prevent the output from toggling.

Pads for 0402-size resistors are available on the AD8159 evaluation board, but the resistors are not populated. Pull-down resistors should not be installed on active channels because a static offset voltage at the input induces duty-cycle distortion (DCD).

### **ORDERING INFORMATION**

#### **ORDERING GUIDE**

| Model          | Description                        |

|----------------|------------------------------------|

| AD8159-EVAL-DC | AD8159 DC-Coupled Evaluation Board |

| AD8159-EVAL-AC | AD8159 AC-Coupled Evaluation Board |

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# NOTES

## NOTES

©2007 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. EB06214-0-3/07(0)

www.analog.com

Rev. 0 | Page 8 of 8